HBM疯涨的幕后推手:CoWoS封装产业链全面爆发

一、算力“堵车”的真相

近期,HBM(高带宽存储芯片,提供高速数据读写)价格持续上行。多轮调价叠加容量与层高升级,整体价格中枢显著抬升,部分型号阶段涨幅接近数倍。但真正让产业链焦虑的,不是价格,而是——有HBM,却没人能封。

上周和一位深耕半导体的基金经理聊起这个问题,他摊手笑道:

“现在拿着钱买HBM颗粒不难,难的是找不到能封装的产能。”

这并非夸张。按多家机构测算,2025年全球HBM需求将超过1亿GB,而CoWoS封装产能缺口仍在30%~40%之间。换句话说,全球相当一部分AI芯片可能卡在“封不进去”的环节上。

想象一座城市:道路拥挤、楼越盖越高,电线交错如麻。这座城市,就是传统芯片。再往上修楼(提升制程)成本高到离谱,性能提升却越来越有限。于是,工程师换了个思路——别再挤在一块地上盖摩天楼,改为建城市群,用立体交通把各个城区连起来。

这套“立体交通系统”,就是CoWoS(芯片-晶圆-基板叠层封装技术)。它让GPU(图形处理器,负责并行计算)与HBM之间,像城市互通高速公路一样,高速协同、低延迟。

真正的算力瓶颈,不在芯片本身,而在它们之间的连接方式。

二、为什么CoWoS会成为AI芯片的“主流方案”

很多人盯着HBM(高带宽存储)的涨价,却忽略了更深层的问题:

HBM能存,但要“喂”给GPU算,必须有高带宽、低延迟的互连通道。

传统封装的连线方式太“慢”,而AI训练需要的是数据的“高速公路”。

这时,CoWoS(芯片-晶圆-基板叠层封装技术)成为目前较成熟、量产规模最大 的解决方案。

它的核心思路不是让芯片更小,而是让连接更高效。

三项关键点,让CoWoS成为AI算力提升的现实选项:

第一,高速互连

CoWoS在GPU与HBM之间加入一层硅中介层(介于芯片与基板的高密度互连结构),上面布满硅通孔(垂直贯穿晶圆的微通道)与微凸块(微米级金属连接点)。

相比传统引线封装,信号传输距离更短、带宽提升约一个数量级——英伟达H100、AMD MI300等高端芯片正是依靠这种2.5D架构实现多颗HBM的并行读写。

第二,更好散热

AI芯片的功耗密度极高,CoWoS采用高导热陶瓷基板和热膨胀匹配的硅中介层,大幅提升热稳定性。实际工程数据显示,采用该封装的芯片在高负载下更易维持满功率运行。

第三,更高密度

CoWoS通过垂直堆叠HBM与GPU,显著节省空间。相同机柜可容纳更多芯片,降低机房冷却与布线成本。

CoWoS并非唯一方案,却是当前算力时代“可行、可量产、最稳”的现实路径。也正因如此,它成为AI芯片与HBM集成的主流技术路线。

三、台积电的封装帝国与全球产能焦虑

HBM是明星,但CoWoS才是幕后导演。没有CoWoS,HBM涨价也没用——它封不上。

按TrendForce与富邦投资资料,2024年底全球CoWoS月产能约4~5万片,2025年底可望增至7万片,2026年底进一步至9万片左右。

但需求增速更快,预计2025年仍存在30%~40%的缺口。

这是一场“算力被封装产能拖后腿”的战争。

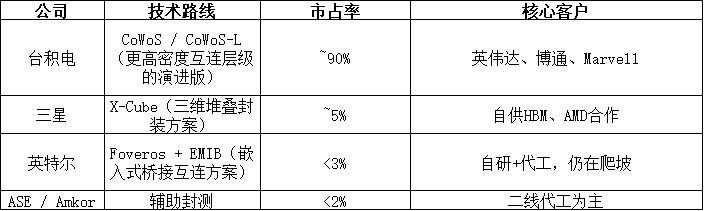

全球格局:谁握住“算力喉咙”

技术门槛极高:硅中介层良率、65纳米光刻瓶颈、晶圆翘曲、热压键合(高温贴合工艺)……任何环节失误都可能整片报废。

台积电虽然加速扩产,但优先保障英伟达订单。英伟达H100、H200系列占掉台积电CoWoS产能近半,Blackwell平台推出后还将转向CoWoS-L制程。

英伟达的瓶颈,不在GPU,而在台积电的封装线。

四、机会在哪?

产业的每一次瓶颈,都是下一轮资本集中的起点。

现在的CoWoS,正处在这样的确定性周期。

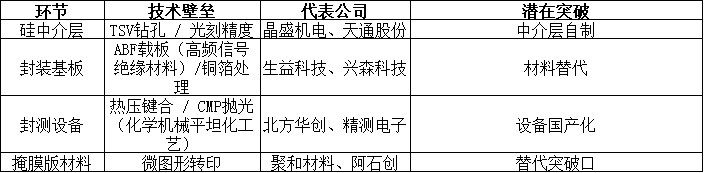

方向一:国产封测厂的突围窗口

长电科技、通富微电、华天科技 三家已建成2.5D/3D封装产线,实现类CoWoS技术的小批量量产。它们在封测总市场中的合计份额超过20%,正在承接国内AI芯片厂(寒武纪、沐曦、壁仞)需求。

逻辑很简单:前道制程受限,后道封装成了现实突破口。

一旦国产GPU订单释放,这几家将是最直接的受益者。

当设计被堵死,封装就是生门。

方向二:核心材料与设备商的“隐形钻石”

目前CoWoS-L制程国产化率不足15%,但每突破一个环节,市场空间都是倍数级扩张。机构预计,未来三年国内中介层设备与封装材料的年复合增速或超40%。

CoWoS的真正红利,不在成品,而在材料。

方向三:AI服务器的“溢出红利”

CoWoS提升封装密度,也让AI服务器结构、电力与散热体系全面升级。算力越密集,系统改造越彻底。

AI液冷、电源系统、PCB载板都将受益:

液冷:科华数据、英维克、银轮股份;

电源:科士达、台达电子;

PCB载板:生益科技、胜宏科技、景旺电子。

封装密度每提升一倍,下游市场就会扩出一个新赛道。

五、从CoWoS到SoIC:算力进入“立体时代”

CoWoS是2.5D封装的巅峰,但技术不会停在这里。下一个阶段,叫SoIC(系统级集成芯片堆叠技术)——真正的三维封装,把芯片从“肩并肩”变成“叠罗汉”。

SoIC的逻辑更激进:把不同功能芯片垂直堆叠,通过混合键合 (无需凸点的直接金属互连)实现纳米级传输。这样一来,信号距离再缩短十倍以上,功耗更低、带宽更宽。

台积电、三星、英特尔都在推进这条路线。SoIC能在三维空间堆叠运算单元,带宽提升、功耗下降。未来,CoWoS和SoIC可能形成分层共存格局:前者主攻AI GPU与HBM配合的大带宽互连,后者用于高端CPU、NPU等多芯片垂直整合。

再往后,是Chiplet(小芯片模块化设计)时代。不同厂商可以分别生产逻辑、存储、I/O模块,再通过先进封装拼装成完整系统。芯片不再是一整块巨石,而是由算力积木拼出的体系。

摩尔定律的尽头,是空间定律。CoWoS是2.5D的门票,SoIC才是三维世界的通行证。

六、结语

过去十年,芯片靠制程往前走;未来十年,AI算力要靠封装往上走。

当制程工艺逼近2纳米物理极限,封装已成为唯一能“扩容”的维度。

CoWoS,就像为算力世界修建了一张立体地铁网。数据不再在“地面”堵车,而是在三维空间自由穿行。SoIC和Chiplet的到来,会让这张“地铁图”更加复杂,却也更加高效——算力在不同模块之间自由流动,形成真正的算力网络。

这场变革的核心,是协同而非极限。未来的芯片竞争,不是谁晶体管更多,而是谁的“连接方式”更聪明。

摩尔定律解决了“能装多少”,CoWoS解决了“能跑多快”,而SoIC正在解决“能拼多大”。这场看不见的封装革命,正在决定AI产业的速度、成本与格局。

当你看到HBM价格节节攀升,其实那是CoWoS和SoIC在背后,重新定义算力的世界。